北卡罗来纳州立大学伊利诺伊大学伊利诺伊州厄巴纳 - 香槟和格鲁吉亚科技正在形成一个中心,旨在加快微电子电路和系统的设计和验证,降低微电子产品制造商的开发成本和上市时间,特别是集成电路。该中心通过国家科学基金会资助五年来工业/大学合作研究中心(I / UCRC)计划,并由该中心的工业成员。

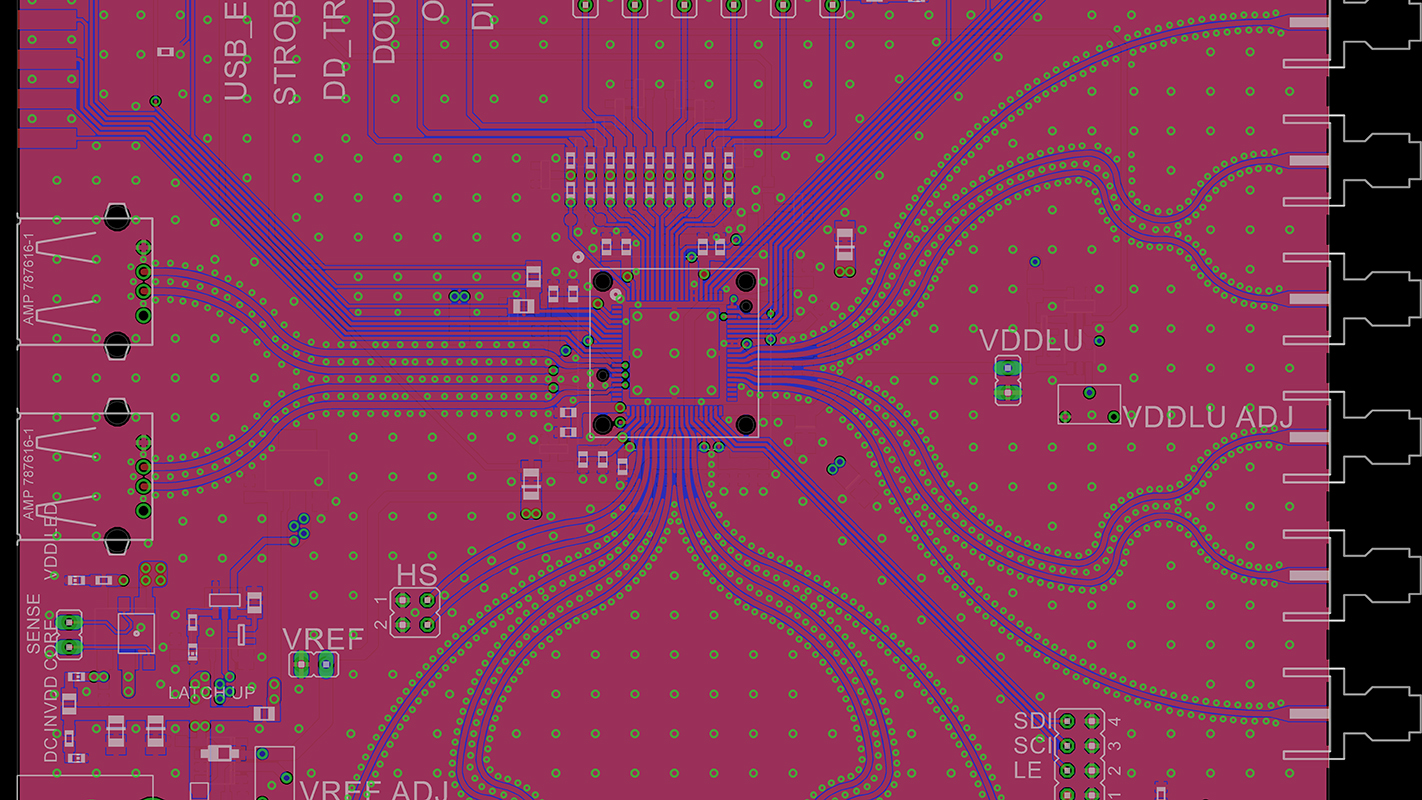

集成电路或芯片,从智能手表到超级计算机的所有内容。半导体行业 - 多年生态的最优出口国 - 一直在寻找新的方式来提高性能,同时降低芯片尺寸和开发成本。

新的通过机器学习的先进电子设备中心(CAEML)将寻求通过利用机器学习技术来开发新型电子设计自动化(EDA)工具的新型号,为批量生产创建和验证芯片设计来加速机器学习技术。

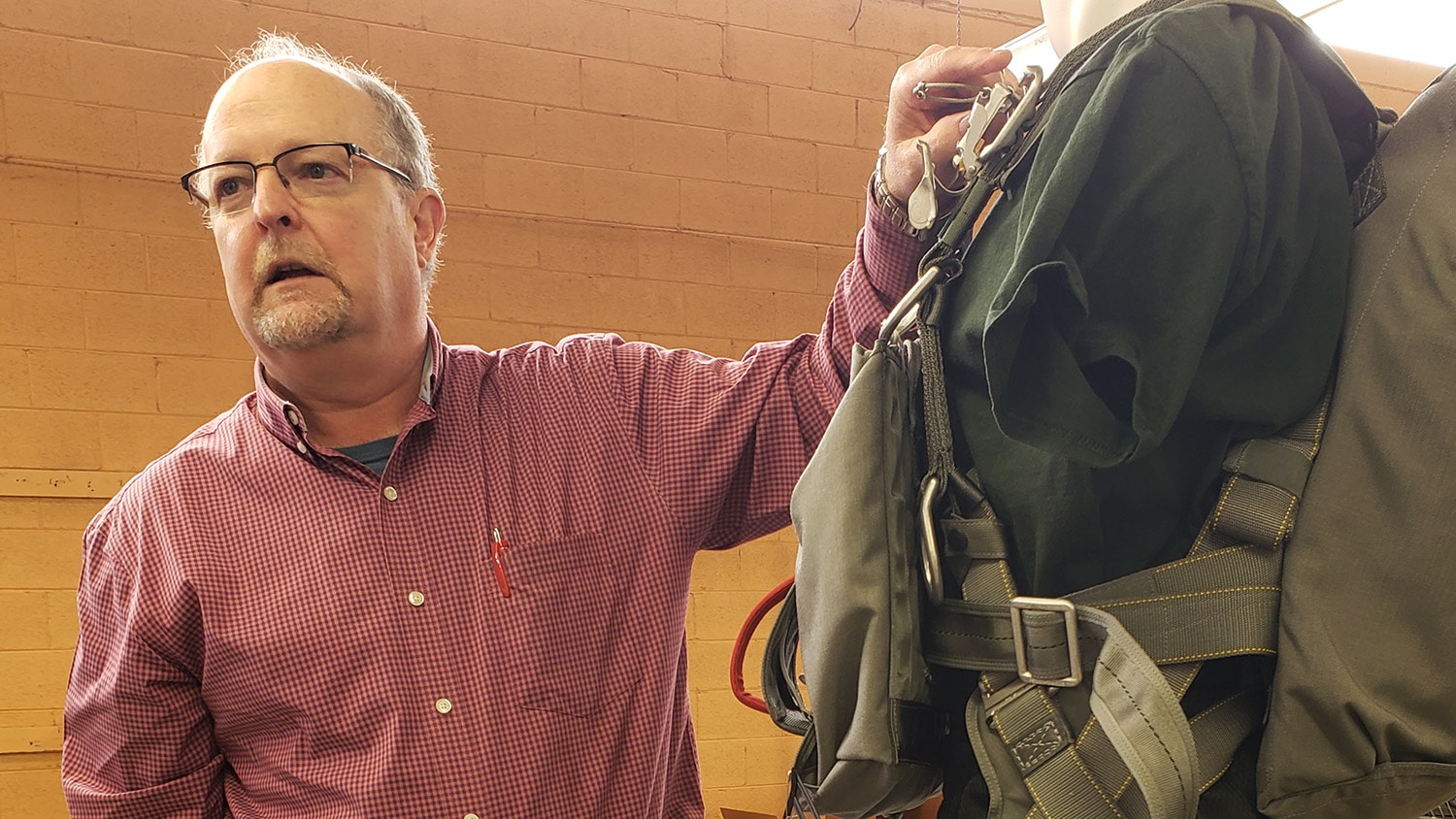

集体目标是创建一个系统,使设计评估过程更容易,说保罗·弗朗松是NC状态的电气工程和Caeml网站领域的杰出教授。

“我喜欢说硅芯片是男人制造的最复杂的伪像,”弗兰扎恩说。“芯片中有数十亿个组件 - 它是令人难以置信的。我们正在创建有助于处理这些复杂性的模型,以便当我们设计芯片时,我们将它们设计为第一次工作。“

目前,芯片制造商在其设计中优化功率,性能,可靠性和成本,因为分析混合太大,以及时地执行。研究人员旨在通过采用芯片的行为或输出的行为模型来克服当前限制而不是物理模型描述的内部流程(这是当今设计流中最常用的类型)。

“当产品失败资格测试时,它通常归因于EDA工具所采用的模型中的缺点,”Illyse Rosenbaum(伊利诺伊州电气计算机工程教授)表示。“在进入市场之前,许多产品必须通过至少一次重新旋转,导致失去金钱和时间。”

CAEML团队将创建一种用于生成行为模型的系统方法,该行业在过去的成功中只有有限。该工作将借鉴机器学习领域的深网络,联想存储和其他研究领域。

研究人员将采取全面的方法,开发适用于大型系统的方法,了解大多数微电子系统由仅仅是单个芯片组成。Madhavan Swaminathan,Gehavan Swaminathan,佐治亚理工学教授和Caeml网站总监Madhavan Swaminathan(Geeml Site总监Madhavan Swaminathan)的说法,即使是一个包装和半导体芯片而言,系统性能也受到两者之间的相互作用。

“通过芯片与包装之间的界面通过集成消失,如系统内部技术,系统需要全面设计,建模和优化,”Swaminathan说。“我们在CAEML中的目标是以一种方式解决系统,即知识产权可以受到保护和重新旋转最小化。”

作为I / UCRC,CAEML将与公司密切合作,这将有助于评估和选择项目。公司联系将使研究人员能够了解制造商面临的现实世界问题,并提供学术界和工业之间的思路。该中心的行业成员包括主要半导体,EDA和网络公司以及政府研究实验室,也将有助于为该中心的工作提供资金;目前,11家公司致力于第一年致力于550,000美元。NSF每年将额外拨款450,000美元。